AMD ha già ricevuto i primi chip Zen 6 funzionanti a 2nm, con ancora mesi prima del lancio commerciale

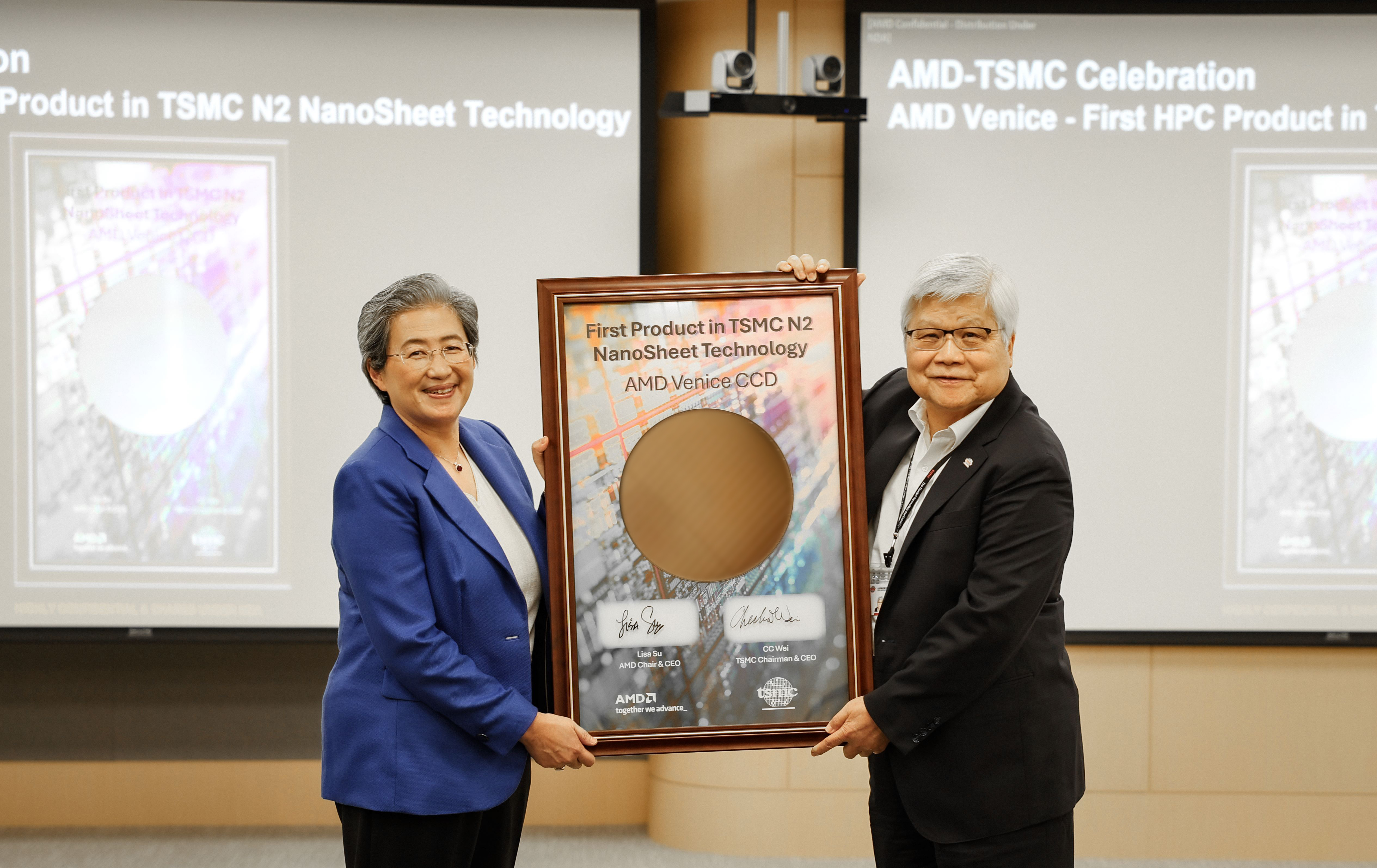

Mentre Intel continua a lottare e a posticipare il rilascio dei nuovi Xeon, AMD ha annunciato inaspettatamente di aver già ricevuto i primi cristalli funzionanti fabbricati con un processo a 2nm. Si tratta del CCD (core) per la prossima generazione di processori EPYC Venice basati sull'architettura Zen 6.

Ecco Cosa Sappiamo

AMD ha confermato che i chip hanno superato con successo i test iniziali e l'alimentazione, ovvero sono "attivi e funzionanti". Sono fabbricati presso la fabbrica TSMC utilizzando il nuovo processo N2, che impiega transistor Gate-All-Around (GAA), il passo successivo dopo FinFET.

Secondo TSMC, il nuovo processo può ridurre il consumo energetico del 24-35% o aumentare le prestazioni del 15% mantenendo lo stesso consumo energetico. Permette anche di posizionare più transistor sulla stessa area (plus 15% di densità rispetto alla generazione a 3nm).

I processori Venice saranno disponibili nel 2026 e faranno parte della 6a generazione di EPYC. Inoltre, AMD ha confermato di aver già testato i chip EPYC di 5a generazione fabbricati presso la nuova Fab 21 di TSMC in Arizona, il che significa che l'azienda sta seriamente diversificando la propria capacità produttiva, una buona notizia in mezzo all'turbamento globale della catena di approvvigionamento.

Il CEO di AMD, Lisa Su, ha definito questo rilascio un esempio di profonda cooperazione con TSMC e il prossimo passo nello sviluppo del calcolo ad alte prestazioni.

Zen 6 è l'architettura futura dei processori AMD che continuerà lo sviluppo della linea Zen. Si prevede che porterà a una riduzione ulteriore della latenza, un miglioramento delle prestazioni della memoria e una scalabilità dei core. Secondo rapporti non ufficiali, Zen 6 utilizzerà una nuova topologia della cache e un microarchitettura FP-block aggiornata.

TSMC N2 è un processo avanzato a 2nm che utilizza transistor GAA (Gate-All-Around) per la prima volta. Ciò consente minori perdite di corrente, frequenze più elevate e minori consumi energetici.

Fonte: ir.amd.com